وریفای کردن طراحی PCB (قسمت #8 آموزش آلتیوم دیزاینر)

این قسمت هشتم از سری آموزش های رایگان آلتیوم دیزاینر است. در این قسمت شما باید نرم افزار آلتیوم دیزاینر را دانلود و نصب کرده باشید و قسمت های قبل را مطالعه کرده باشید.

قسمت قبلی: قرار دادن قطعات و مسیرکشی برد (قسمت #7 آموزش آلتیوم دیزاینر)

ویرایشگر PCB یک محیط طراحی مبتنی بر قوانین است که در آن میتوانید انواع مختلفی از محدودیتهای طراحی را تعریف کنید تا از صحت و یکپارچگی برد خود اطمینان حاصل کنید. ویژگی بررسی قوانین آنلاین (Online DRC) هنگام کار، قوانین فعال را پایش میکند و بهصورت فوری هرگونه تخلف یا مغایرت طراحی را مشخص مینماید. بهصورت جایگزین، میتوانید بررسی دستهای قوانین (Batch DRC) را اجرا کنید تا مطمئن شوید طراحی با تمام قوانین مطابقت دارد و گزارشی شامل قوانین فعال و تخلفات شناساییشده دریافت کنید.

در مراحل قبل از این آموزش، برخی از محدودیتهای طراحی مانند فاصله الکتریکی (Electrical Clearance)، عرض مسیر (Routing Width) و سبک ویا (Routing Via Style) را بررسی و تنظیم کردید. علاوه بر این موارد، مجموعهای از قوانین طراحی دیگر نیز بهصورت خودکار هنگام ایجاد یک برد جدید تعریف میشوند.

بررسی قوانین طراحی (Design Rule Check)

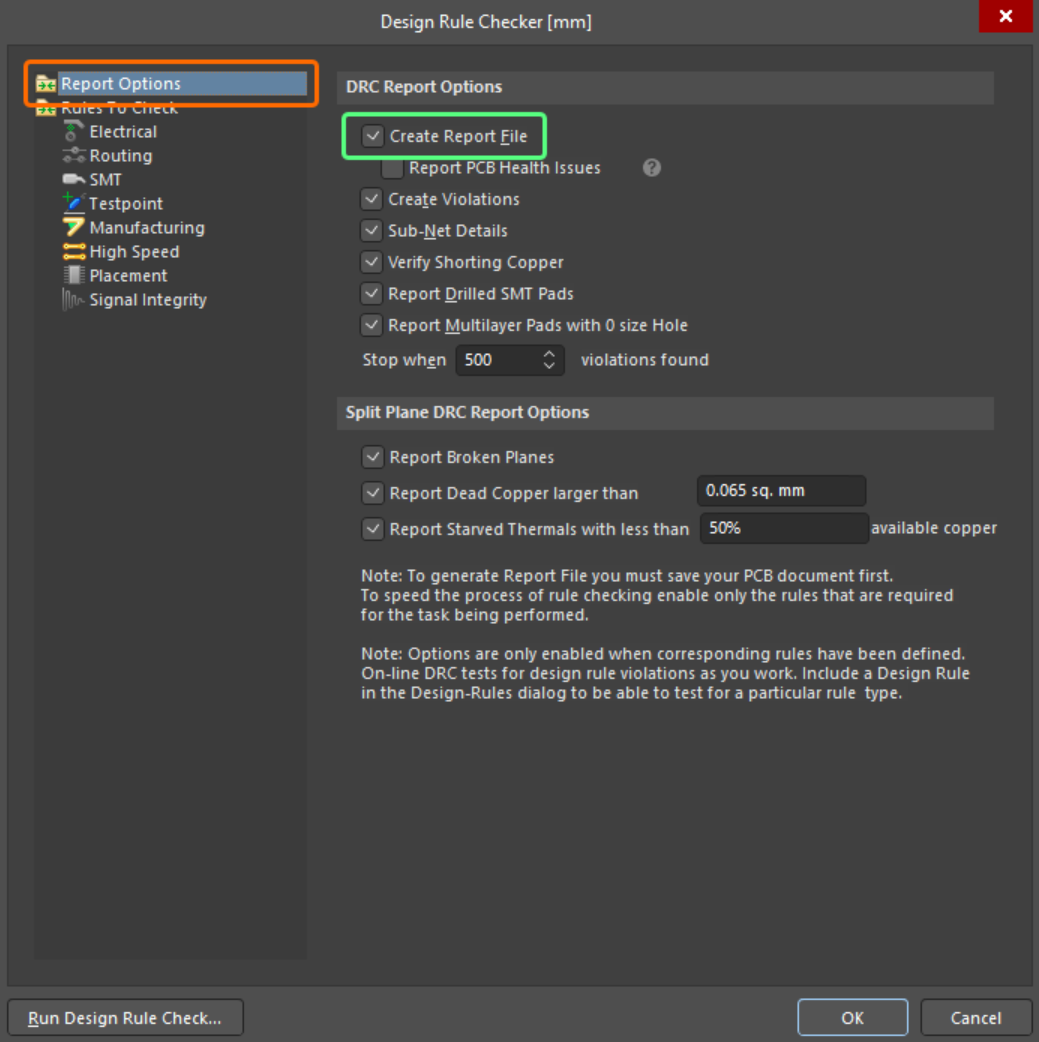

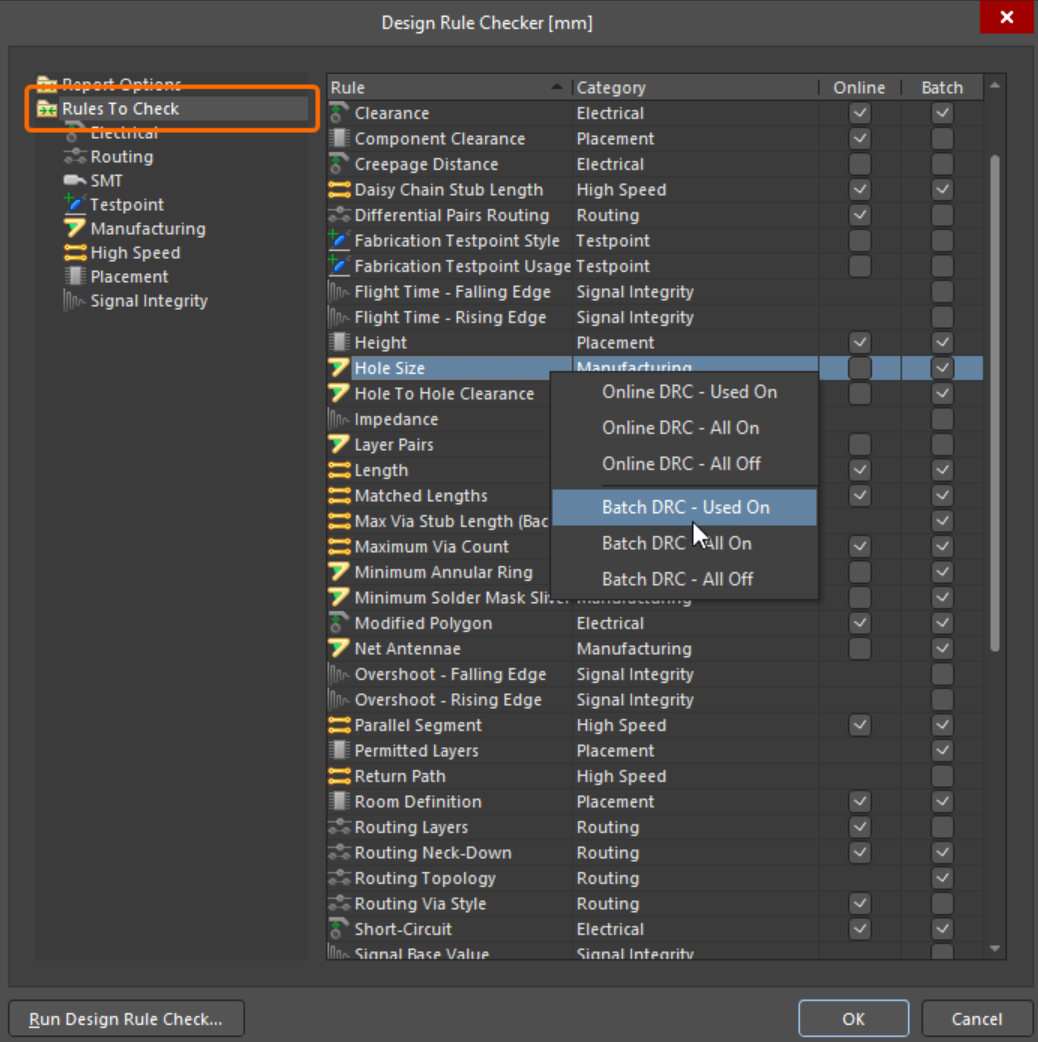

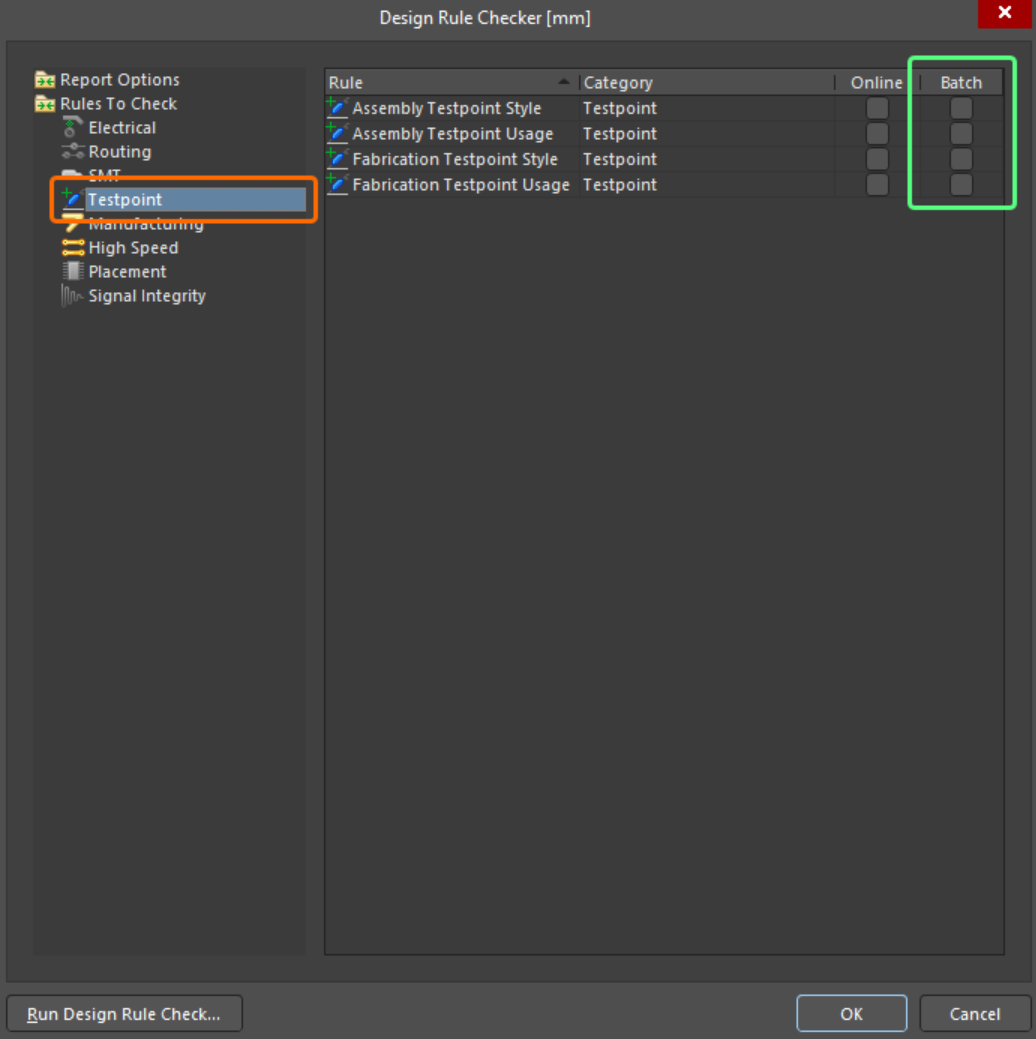

طراحی از طریق اجرای بررسی قوانین طراحی (DRC) برای یافتن تخلفات بررسی میشود. هر دو نوع DRC آنلاین و DRC دستهای (Batch DRC) در پنجره Design Rule Checker پیکربندی میشوند. برای باز کردن این پنجره، از مسیر Tools » Design Rule Check در منوی اصلی استفاده کنید.

در این پنجره، میتوانید گزینههای کلی گزارشدهی را در بخش Report Options و تنظیمات مربوط به قوانین خاص را در بخش Rules to Check انجام دهید.

برای اجرای بررسی قوانین طراحی، روی دکمه Run در پایین پنجره کلیک کنید. پس از اجرای DRC، پنل Messages باز میشود و تمام تخلفات شناساییشده را فهرست میکند.

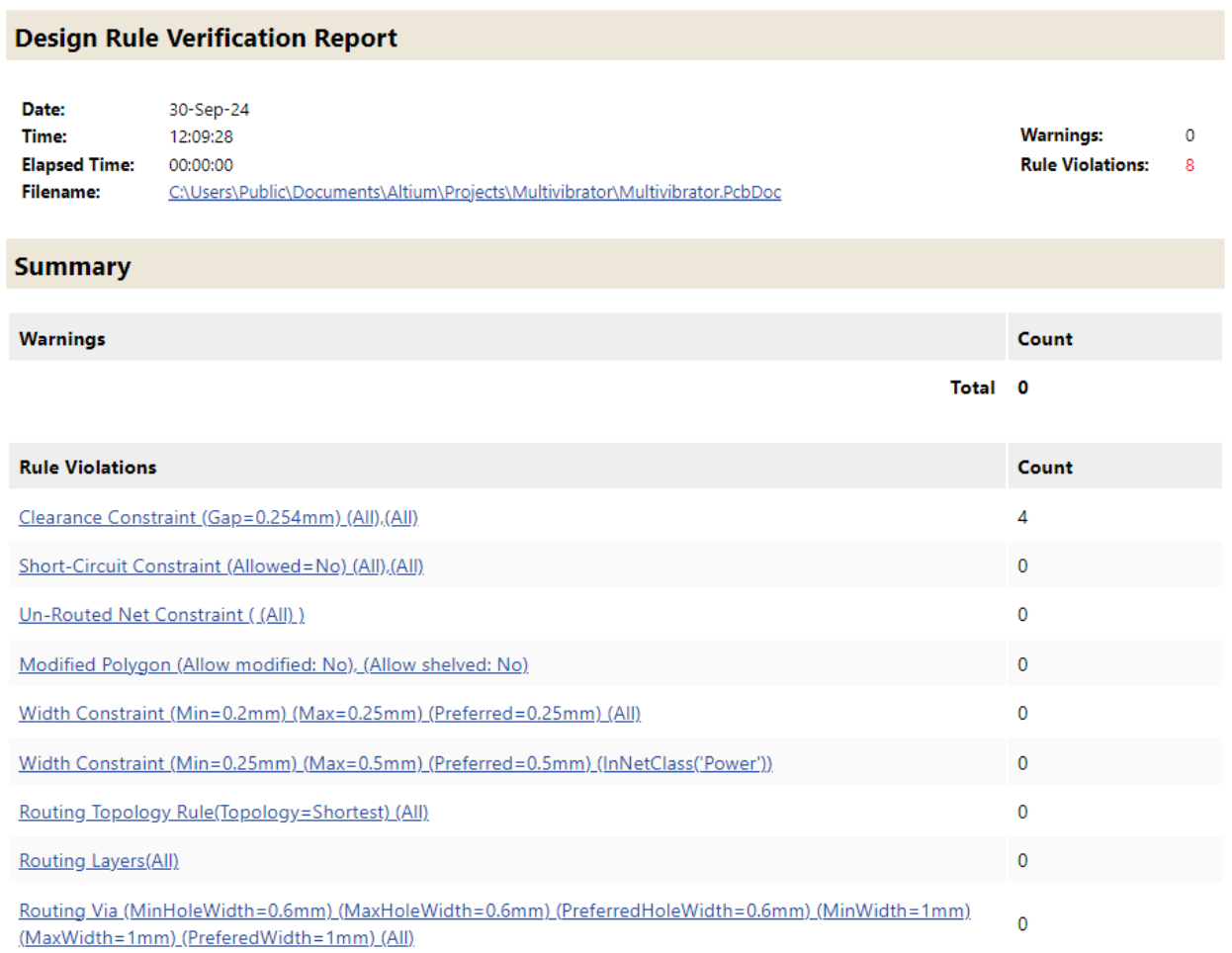

اگر گزینه Create Report File فعال باشد، گزارشی با عنوان Design Rule Verification Report در یک تب جداگانه باز خواهد شد. این گزارش شامل جزئیاتی از قوانین فعال برای بررسی، تعداد تخلفات شناساییشده و اطلاعات دقیق هر تخلف است.

مراحل اجرای بررسی DRC

- از منوی اصلی، دستور Tools » Design Rule Check را انتخاب کنید تا پنجره Design Rule Checker باز شود.

- در صفحه Report Options، اطمینان حاصل کنید که گزینه Create Report File فعال است.

در صفحه Rules To Check، در ناحیه جدول راستکلیک کرده و گزینه Batch DRC – Used On را انتخاب کنید.

در صفحه Rules To Check، در ناحیه جدول راستکلیک کرده و گزینه Batch DRC – Used On را انتخاب کنید.

- بررسی دستهای قوانین مربوط به Testpoint را غیرفعال کنید. برای این کار، بخش Testpoint را از درخت انتخاب کرده و تیک گزینههای Batch در چهار قانون این دسته را بردارید.

- روی دکمه Run در پایین پنجره کلیک کنید تا DRC اجرا شود. پنجره بسته شده و گزارش بهصورت خودکار باز خواهد شد.

محتوای گزارش DRC

گزارش معمولاً شامل موارد زیر است:

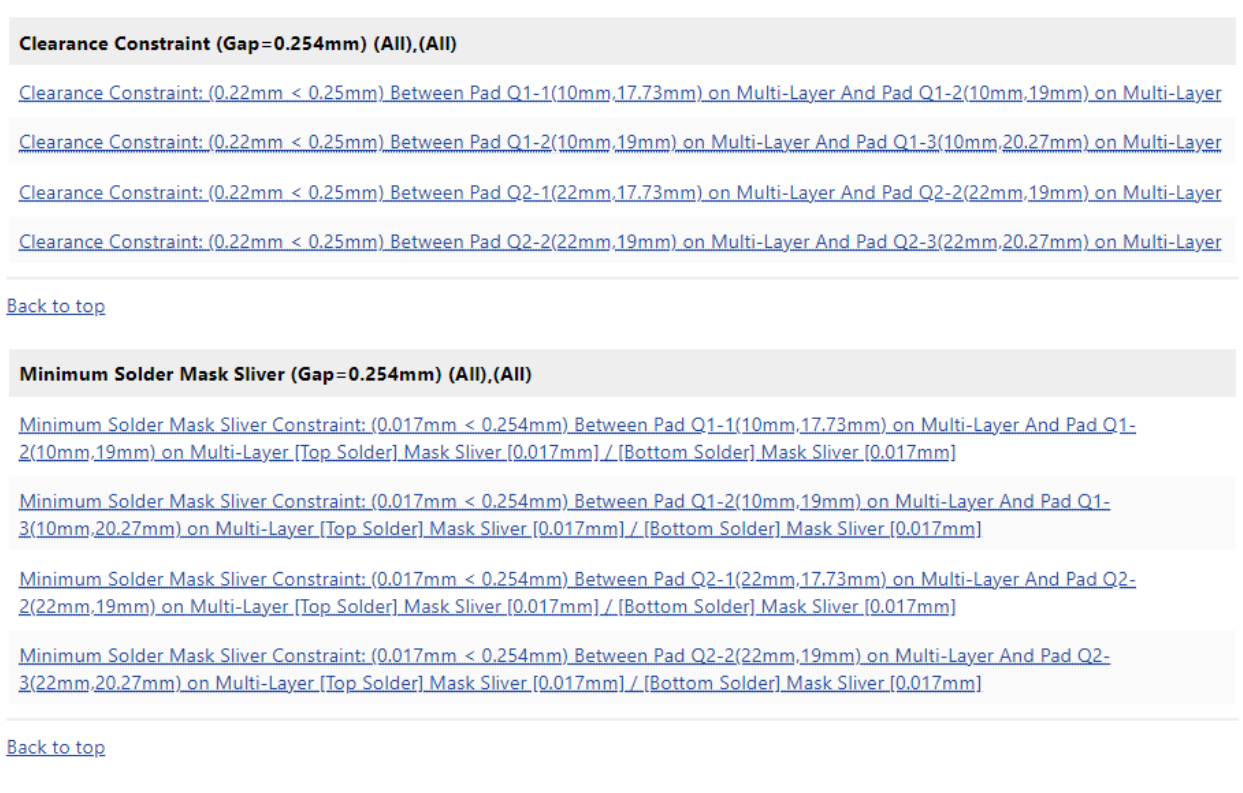

- 4 خطای Minimum Solder Mask Sliver: عرض نوار ماسک لحیم کمتر از مقدار مجاز است.

- 4 خطای Clearance Constraint: فاصله الکتریکی بین اجسام در لایههای سیگنال کمتر از حداقل مقدار تعیینشده است.

بخش بالایی گزارش، قوانین فعال برای بررسی و تعداد تخلفات مربوط به هرکدام را نشان میدهد. با کلیک روی هر قانون، میتوانید مستقیماً به محل آن تخلف در طرح منتقل شوید.

بخش پایینی گزارش، جزئیات هر قانون نقضشده و لیستی از اشیای مربوط به آن را نمایش میدهد. با کلیک روی هر تخلف، مستقیماً به همان شیء در برد PCB هدایت میشوید.

تخلفات شناساییشده همچنین در پنل Messages نیز نمایش داده میشوند.

شناسایی و رفع تخلفات طراحی

به عنوان طراح، شما باید تخلفات موجود در برد مدار چاپی (PCB) را پیدا کنید، شرایط آن را بررسی کرده، میزان اختلاف را بسنجید و سپس بهترین روش را برای رفع آن انتخاب کنید.

نکاتی درباره شناسایی و رفع تخلفات

نرمافزار Altium Designer دو روش برای نمایش تخلفات طراحی ارائه میدهد:

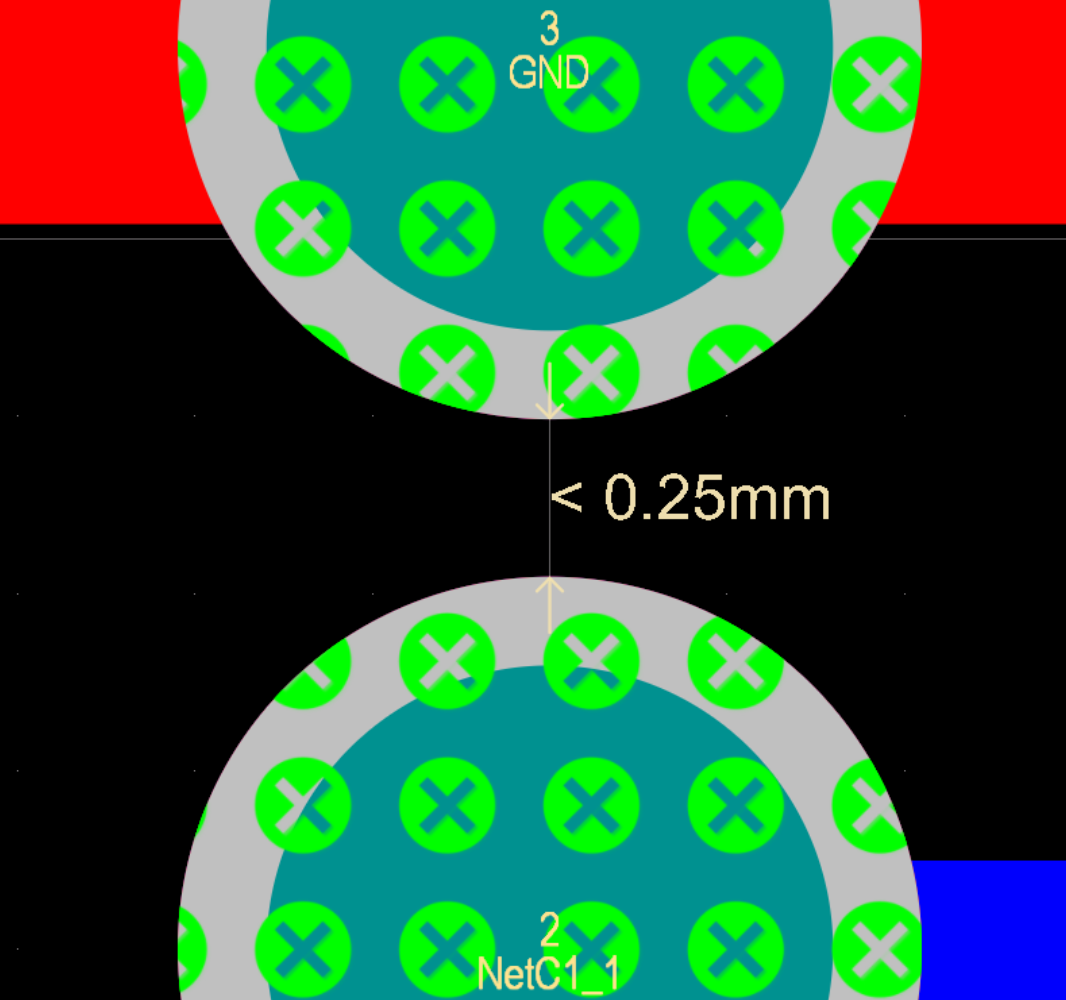

- پوشش تخلف (Violation Overlay): در این روش، اجزای دارای خطا با الگوی خاصی (بهصورت پیشفرض، دایرههای سبز با علامت ضربدر) مشخص میشوند.

- جزئیات تخلف (Violation Details): ماهیت خطا با مقدار عددی (که میزان نقض محدودیت را نشان میدهد) و/یا یک آیکون (که محل و نوع تخلف را مشخص میکند) نمایش داده میشود.

بهعنوان مثال، در تصویر زیر یک تخلف Clearance نمایش داده شده است. در این حالت، پدهای خطادار با الگوهای گرافیکی مشخص شدهاند و همچنین پیکانهای سفید همراه با مقدار <0.25mm نشان میدهند که فاصله واقعی کمتر از مقدار مجاز 0.25 میلیمتر است.

روش پیدا کردن تخلفات

برای یافتن یک تخلف میتوانید:

- روی لینک موجود در بخش پایینی گزارش که جزئیات هر تخلف را نشان میدهد کلیک کنید، یا

- روی ورودیهای مربوط به تخلف در پنل Messages دوبار کلیک کنید.

ورودیهای تخلف در گزارش و در پنل پیامها شامل اطلاعاتی درباره میزان اختلاف نیز هستند.

بهطور مثال، عبارت 0.017mm < 0.254mm یعنی مقدار واقعی فاصله (0.017 میلیمتر) کمتر از حد مجاز (0.254 میلیمتر) است.

رفع تخلفات فاصله (Clearance Violations)

در طراحی آموزشی این مثال، چهار تخلف Clearance بین پدهای ترانزیستور مشاهده شده است.

دو راه برای رفع این مشکل وجود دارد:

- کوچک کردن اندازه پدهای ترانزیستور تا فاصله بین آنها بیشتر شود.

- تنظیم مجدد قانون فاصله تا مقدار مجاز کوچکتری بین پدهای ترانزیستور مجاز شود.

از آنجا که مقدار فعلی (0.25 میلیمتر) نسبتاً زیاد و فاصله واقعی (0.22 میلیمتر) نزدیک به آن است، بهتر است قانون را طوری تغییر دهید که فاصله مجاز کمتر شود.

این راهحل قابلقبول است زیرا تنها قطعهای که پدهای thru-hole دارد، کانکتور است که فاصله پدهایش 1 میلیمتر است.

اما اگر قطعات دیگری نیز شرایط مشابه داشتند، بهتر بود یک قانون فاصله جدید فقط برای پدهای ترانزیستور تعریف شود — مشابه کاری که برای قوانین Solder Mask Expansion انجام میشود.

کدام ابزار برای تنظیم قوانین دارم؟

بسته به نسخه Altium شما، ممکن است یکی از دو گزینه زیر در دسترس باشد:

- Constraint Manager

- PCB Rules and Constraints Editor

برای بررسی، از منوی اصلی Design در هنگام باز بودن فایل PCB استفاده کنید و ببینید کدام گزینه نمایش داده میشود. سپس روش مربوط به همان را دنبال کنید.

رفع خطا از طریق Constraint Manager

مرحلهی اول، کاهش مقدار مجاز عرض شکاف یا Sliver Width است.

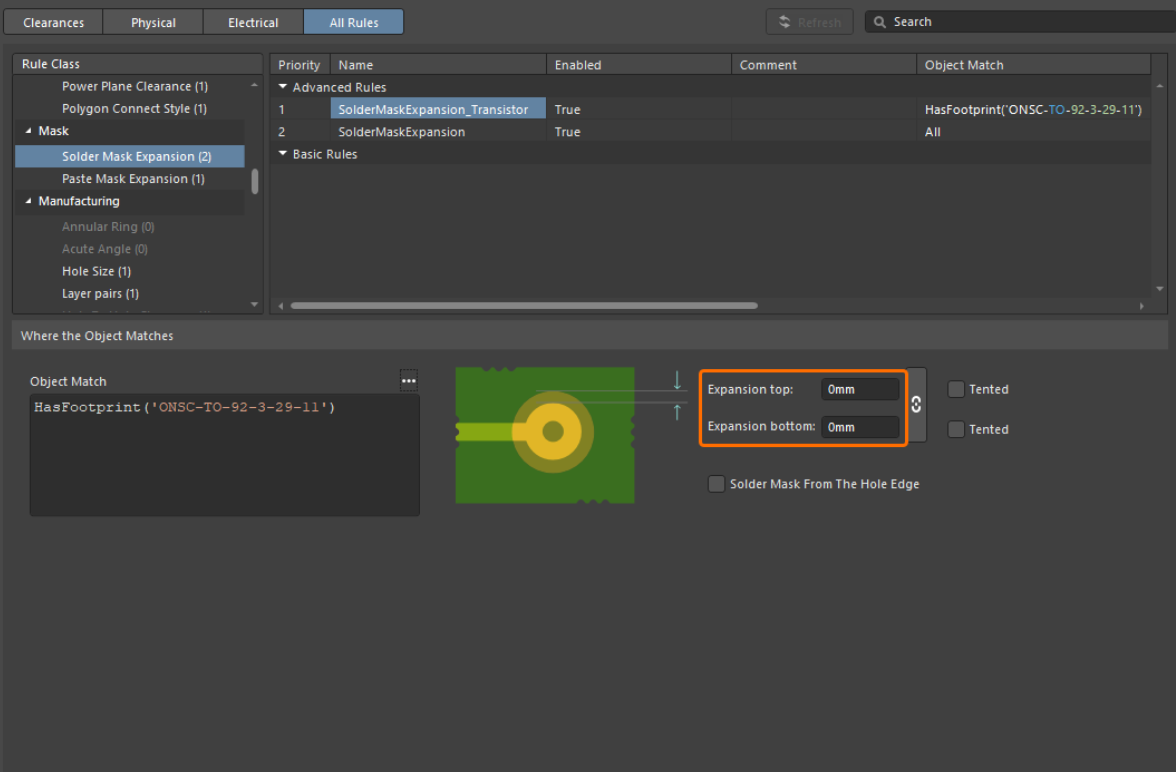

برای انجام این کار، نمای All Rules را در Constraint Manager باز کنید. این گزینه از طریق دکمهی مربوطه در بالای پنجرهی Constraint Manager در دسترس است.

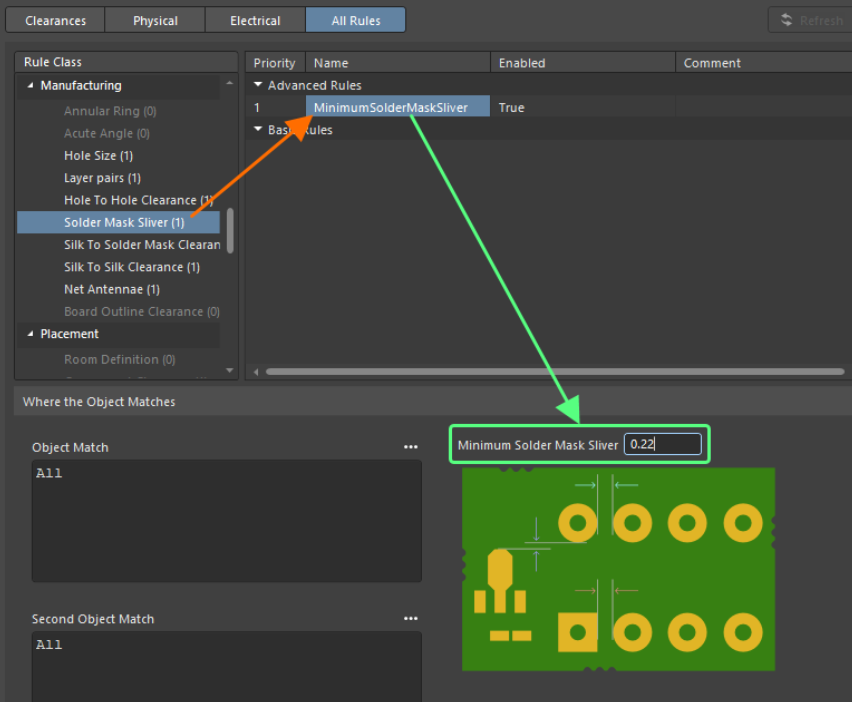

در منوی درختی سمت چپ، وارد بخش Manufacturing شوید و نوع قانون Solder Mask Sliver را انتخاب کنید. سپس در ناحیهی اصلی جدول، قانون موجود با نام MinimumSolderMaskSliver را انتخاب نمایید.

برای چنین طراحی، مقداری برابر با فاصلهی بین پدها یعنی 0.22 میلیمتر (حدود 8.7 میل) قابل قبول است. مقدار Minimum Solder Mask Sliver را در بخش Constraint region قانون روی 0.22 تنظیم کنید.

قانون جدید گسترش ماسک لحیم ترانزیستورها

در مرحلهی بعد، باید قانونی اضافه کنید که گسترش ماسک (Mask Expansion) را فقط برای ترانزیستورها به صفر کاهش دهد.

با این کار، دهانهی ماسک دقیقاً هماندازهی پد میشود و عرض شکاف بین ماسکهای لحیم برابر با فاصلهی میان پدها (یعنی 0.22 میلیمتر) خواهد بود.

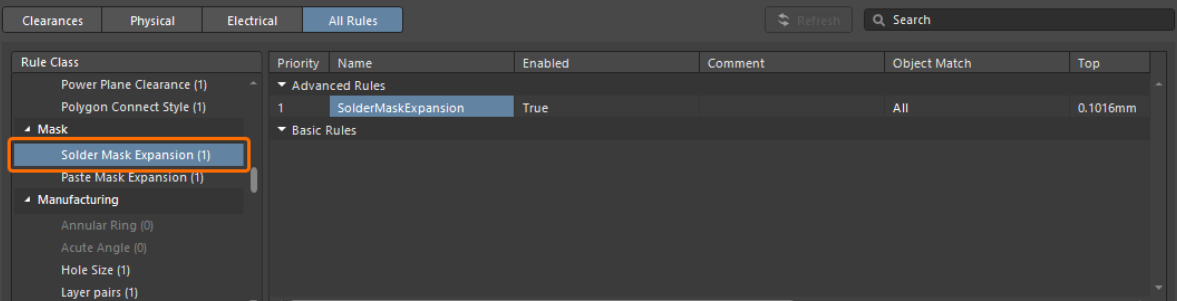

در منوی سمت چپ، از دستهی Mask، نوع قانون Solder Mask Expansion را انتخاب کنید تا قوانین موجود از این نوع نمایش داده شوند.

در اینجا باید قانونی با نام SolderMaskExpansion وجود داشته باشد که مقدار گسترش آن 0.1016 میلیمتر (4 میل) است.

از آنجا که تنها پدهای ترانزیستور دچار خطا هستند، این مقدار را تغییر نمیدهید. در عوض، یک قانون جدید ایجاد خواهید کرد.

برای افزودن قانون جدید Solder Mask Expansion:

- در فضای خالی جدول اصلی کلیک راست کرده و گزینهی Add Custom Rule را انتخاب کنید.

- قانونی با نام SolderMaskExpansion_1 ایجاد میشود.

- روی نام آن دوبار کلیک کرده و آن را به SolderMaskExpansion_Transistor تغییر دهید.

روی قانون جدید کلیک کنید تا تنظیمات آن در پایین پنجره نمایش داده شود.

تعریف محدودهی قانون (Scope)

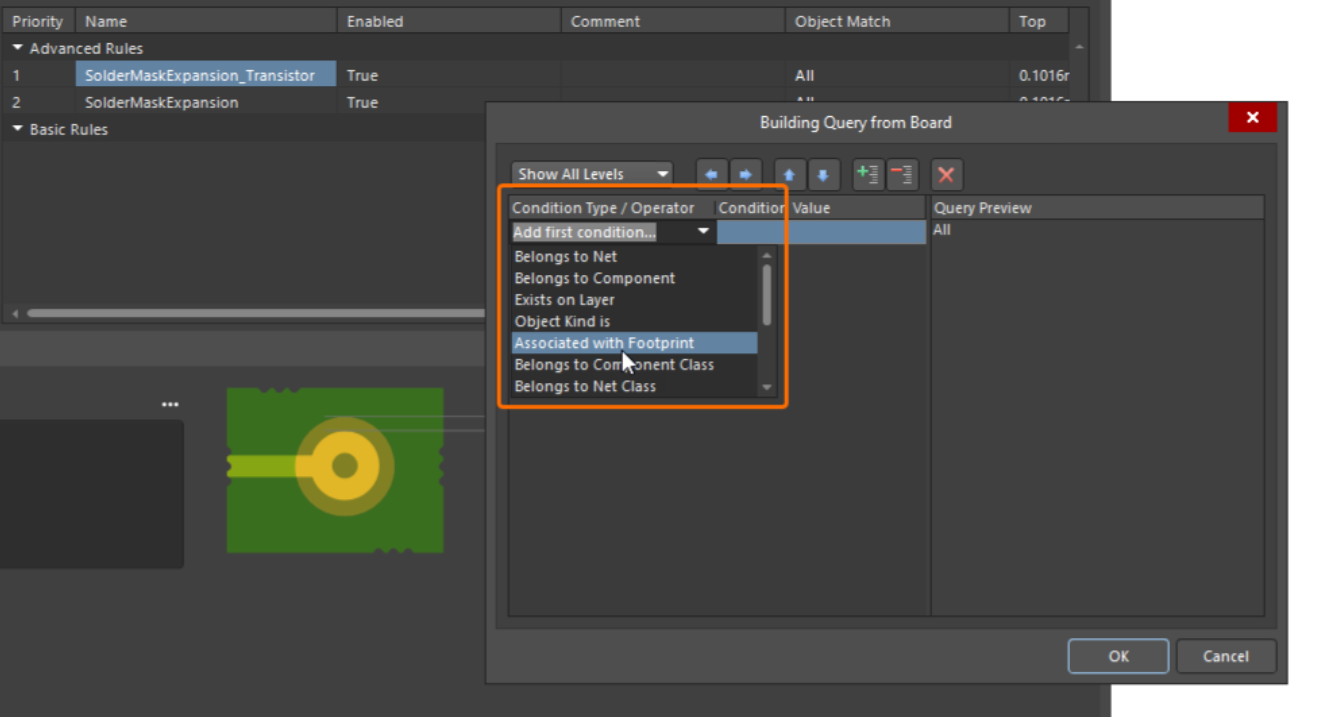

برای تعریف محدودهی قانون، از ابزار Query Builder استفاده کنید:

- روی دکمهی کنار فیلد Object Match کلیک کنید و گزینهی Open Query Builder را انتخاب کنید.

- در پنجرهی Building Query from Board، از ستون Condition Type / Operator گزینهی Associated with Footprint را انتخاب کنید.

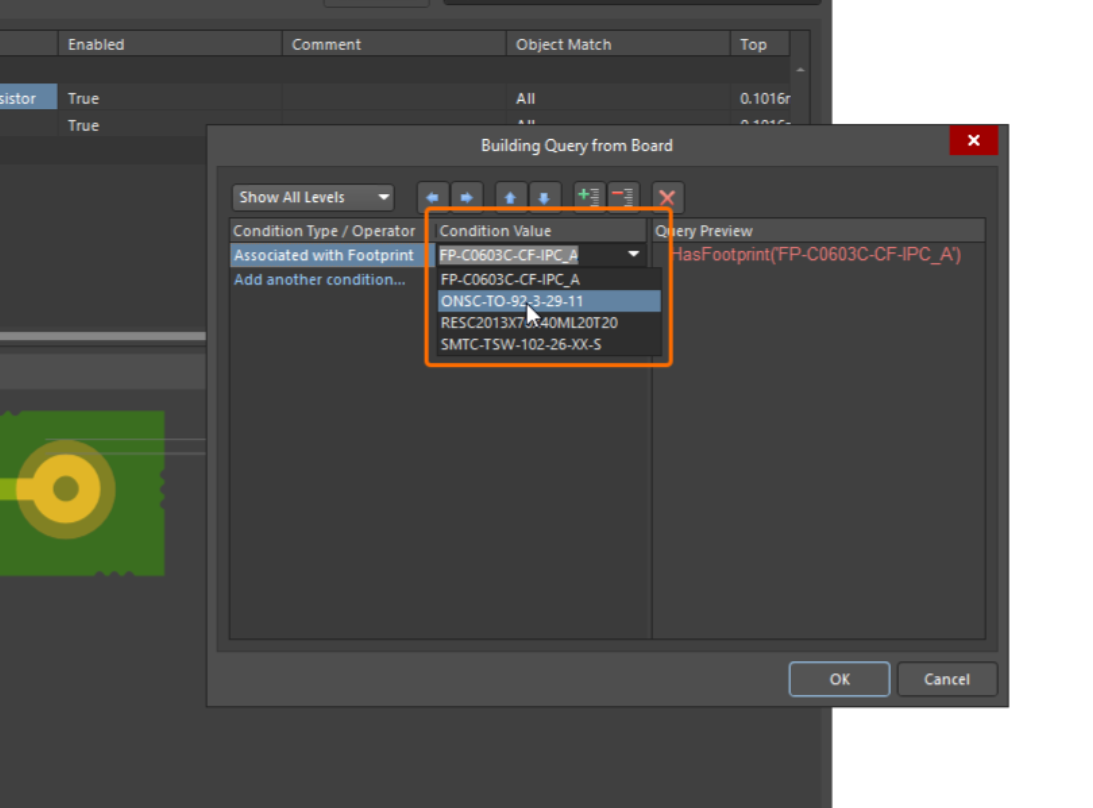

- سپس از ستون Condition Value مقدار ONSC-TO-92-3-29-11 را برگزینید.

- پس از فشردن OK، عبارت زیر در فیلد Object Match ظاهر میشود:

HasFootprint('ONSC-TO-92-3-29-11')

اکنون مقدار Expansion top و Expansion bottom را روی 0 قرار دهید.

حالا باید این تغییرات را ذخیره کنید.

- تغییرات را از مسیر File » Save to PCB ذخیره کنید.

- برای بستن Constraint Manager، روی تب آن در بالای محیط طراحی کلیک راست کرده و گزینهی

Close Multivibrator.PcbDoc [Constraints] را انتخاب کنید. - در نهایت، در Projects panel روی فایل PCB کلیک راست کرده و گزینهی Save را انتخاب کنید تا فایل بهصورت محلی ذخیره شود.

این مراحل باعث میشوند خطاهای Solder Mask Sliver برطرف شده و طراحی مطابق قوانین تولید تنظیم گردد.

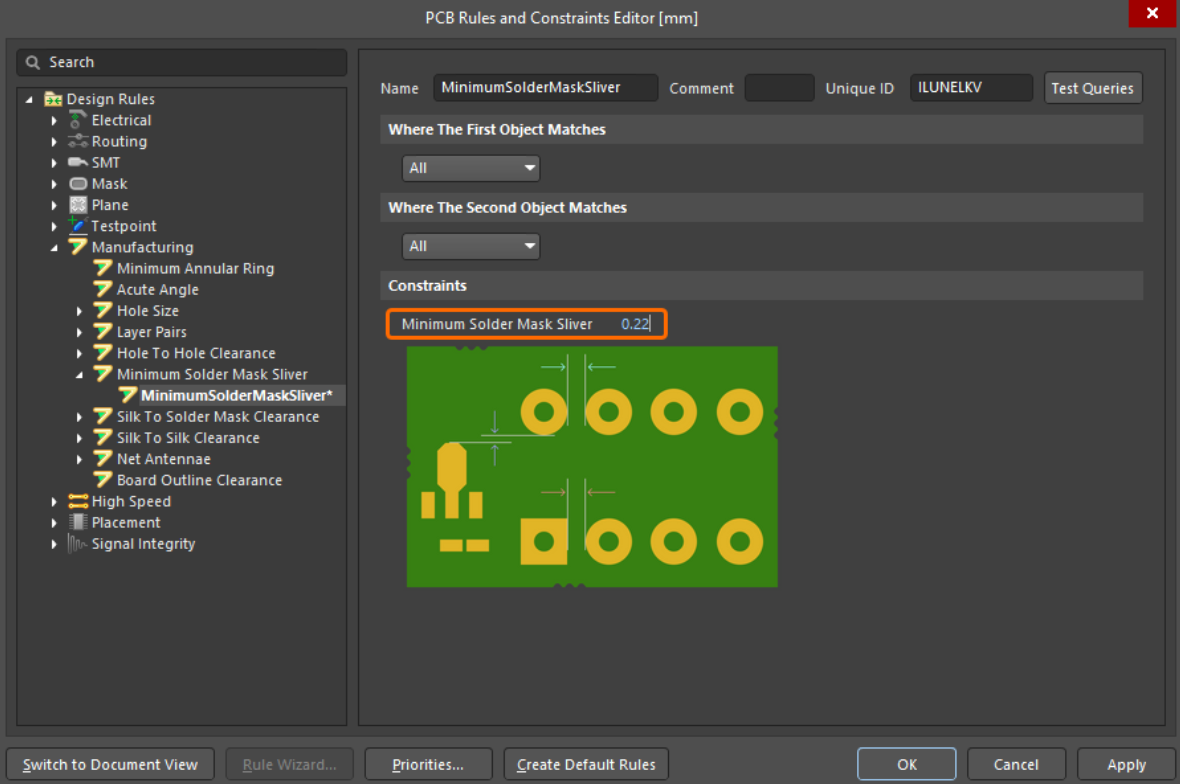

رفع خطای Solder Mask Sliver با PCB Rules و Constraints Editor

مرحله 1: کاهش عرض مجاز شکاف (Sliver Width)

ابتدا باید مقدار مجاز عرض شکاف را کاهش دهید.

برای این کار، در پنجره PCB Rules and Constraints Editor از منوی درختی سمت چپ وارد بخش Manufacturing شوید و قانون موجود با نام MinimumSolderMaskSliver را انتخاب کنید.

برای چنین طراحی، مقداری برابر با فاصلهی بین پدها یعنی 0.22 میلیمتر (حدود 8.7 میل) مناسب است.

مقدار Minimum Solder Mask Sliver را در بخش Constraints روی 0.22 تنظیم کنید.

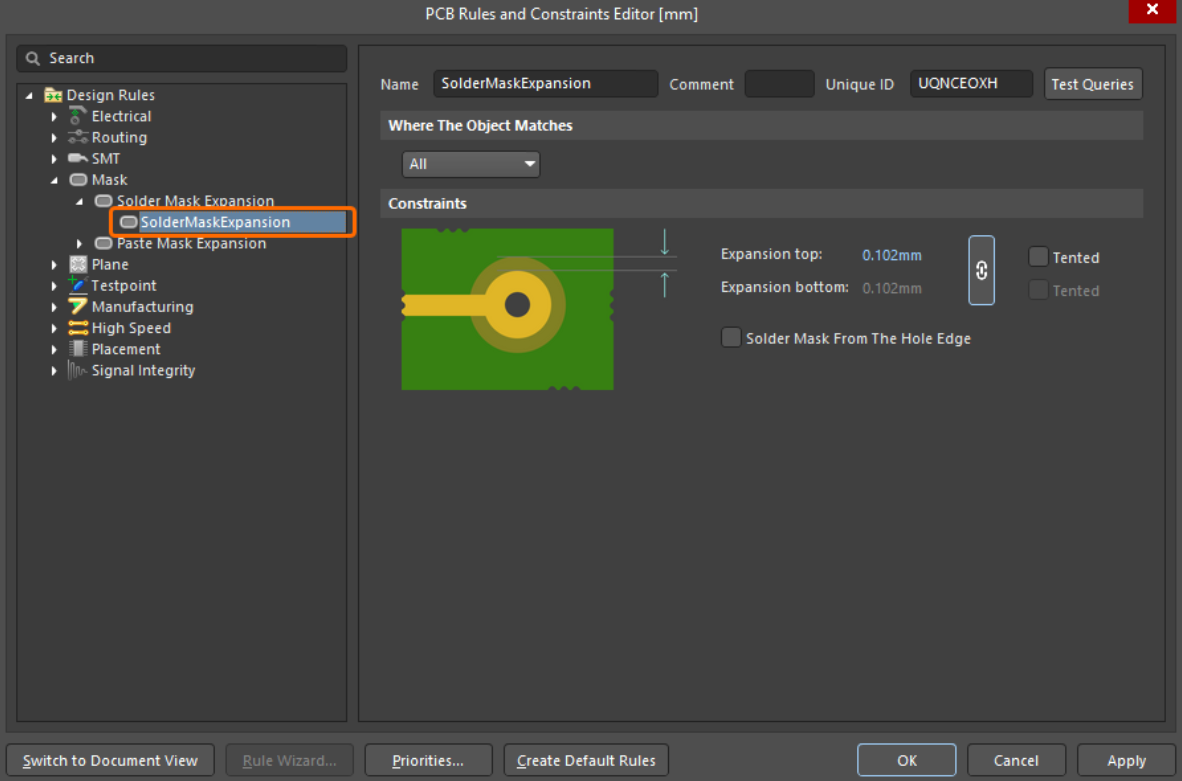

مرحله دوم: قانون برای گسترش ماسک ترانزیستورها

در این مرحله، باید قانونی اضافه کنید که گسترش ماسک لحیم را فقط برای ترانزیستورها به صفر کاهش دهد.

با انجام این کار، دهانهی ماسک هماندازهی پد میشود و در نتیجه عرض نوار ماسک بین پدها برابر با فاصلهی بین آنها یعنی 0.22 میلیمتر خواهد بود.

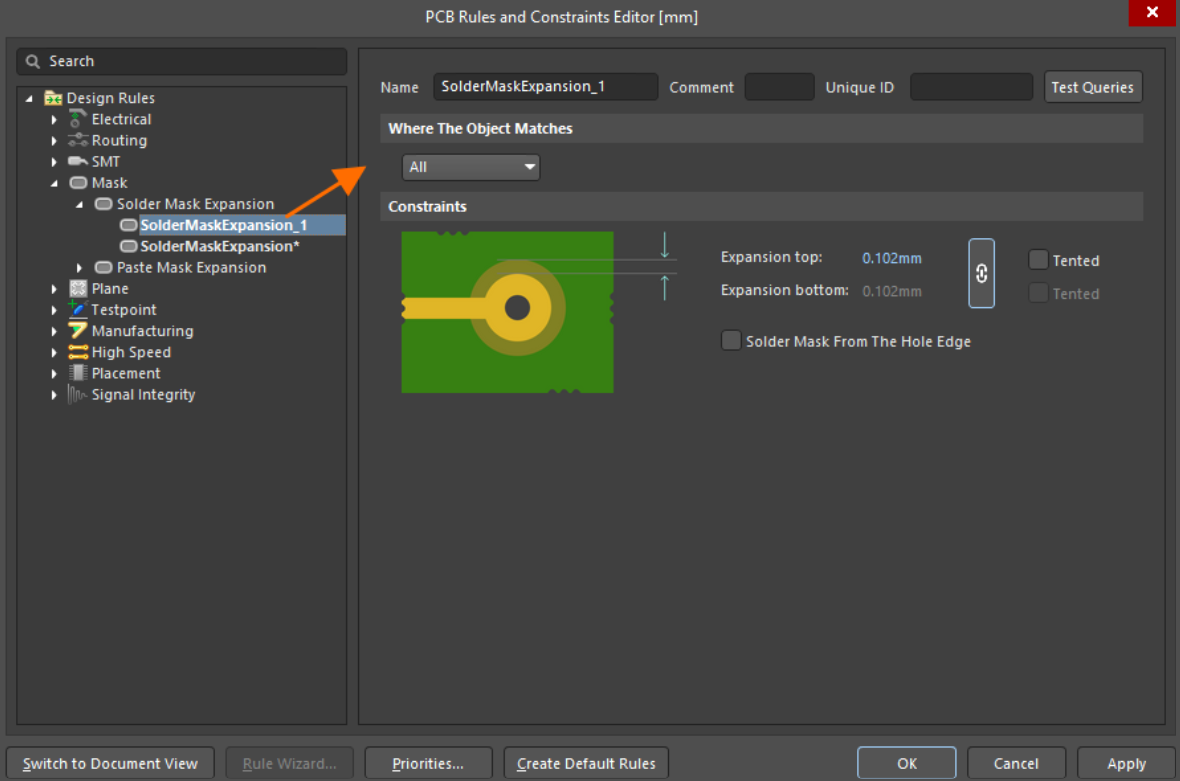

در منوی سمت چپ، بخش Mask را باز کرده و سپس گزینهی Solder Mask Expansion را گسترش دهید.

در اینجا باید قانونی با نام SolderMaskExpansion وجود داشته باشد که مقدار گسترش آن 0.102 میلیمتر (4 میل) است.

از آنجا که فقط پدهای ترانزیستور دچار خطا هستند، این مقدار را تغییر ندهید و بهجای آن یک قانون جدید بسازید.

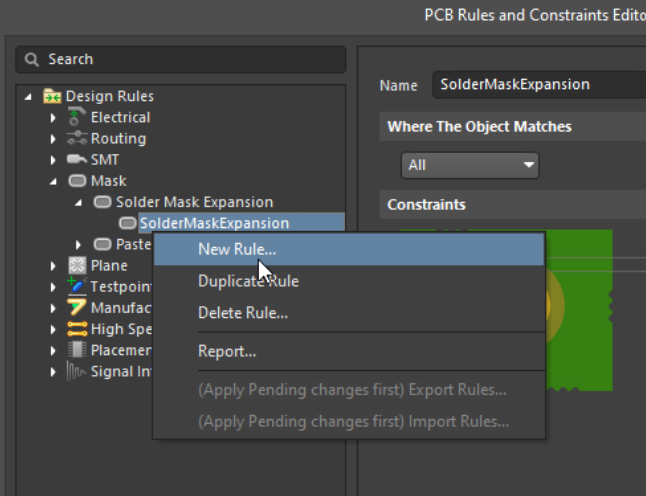

برای افزودن قانون جدید:

- روی قانون موجود SolderMaskExpansion در درخت سمت چپ کلیک راست کرده و گزینهی New Rule را انتخاب کنید.

- قانونی با نام SolderMaskExpansion_1 ایجاد میشود. روی آن کلیک کنید تا تنظیماتش نمایش داده شود.

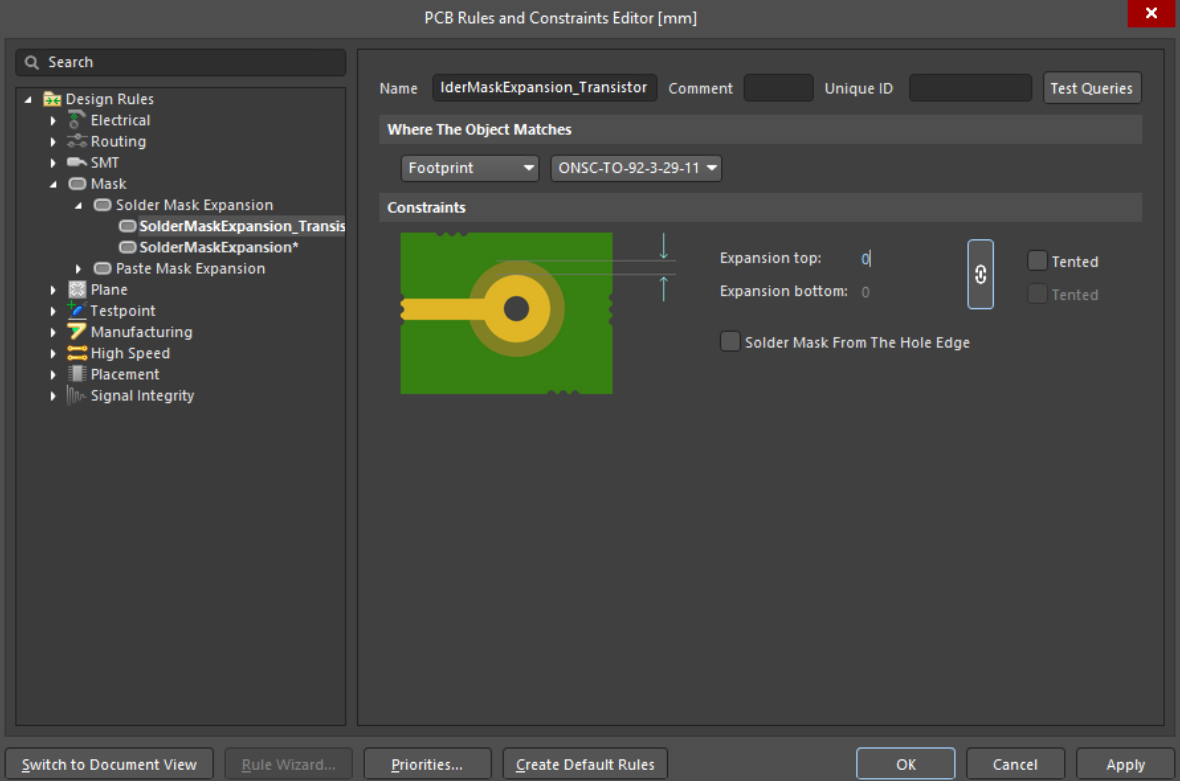

سپس تنظیمات را به شکل زیر تغییر دهید:

- Name: مقدار را به SolderMaskExpansion_Transistor تغییر دهید.

- Where the Object Matches: از منوی کشویی گزینهی Footprint را انتخاب کرده و سپس از فهرست دوم گزینهی ONSC-TO-92-3-29-11 (نام فوتپرینت ترانزیستور) را انتخاب کنید.

- Expansion top / Expansion bottom: مقدار هر دو را روی 0 قرار دهید.

در پایان، روی OK کلیک کنید تا تغییرات ذخیره شده و پنجرهی PCB Rules and Constraints Editor بسته شود.

برای ذخیرهی فایل PCB، در Projects panel روی نام فایل کلیک راست کرده و گزینهی Save را انتخاب کنید تا تغییرات بهصورت محلی ذخیره شوند.

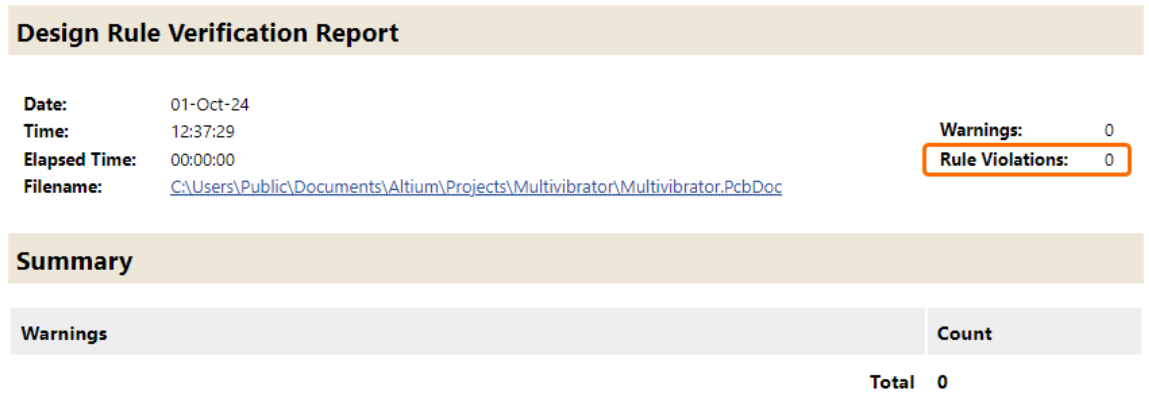

اجرای مجدد بررسی قوانین طراحی (Design Rule Check)

اکنون باید بررسی قوانین طراحی (DRC) را دوباره اجرا کنید تا مطمئن شوید تمام خطاها برطرف شدهاند.

همیشه پیش از ایجاد خروجی نهایی، باید از تمیز بودن گزارش تأیید قوانین طراحی (Design Rule Verification Report) اطمینان حاصل کنید.

از منوی Tools » Design Rule Check وارد گفتوگوی DRC شوید و گزینهی Create Report File را در بخش Report Options فعال کنید. سپس روی دکمهی Run Design Rule Check کلیک کنید.

یک گزارش جدید تولید میشود و در تب جداگانهای باز خواهد شد. مطمئن شوید هیچ خطایی در گزارش وجود ندارد.

اگر هنوز خطایی مشاهده شد، آن را رفع کرده و دوباره گزارش را تولید کنید.

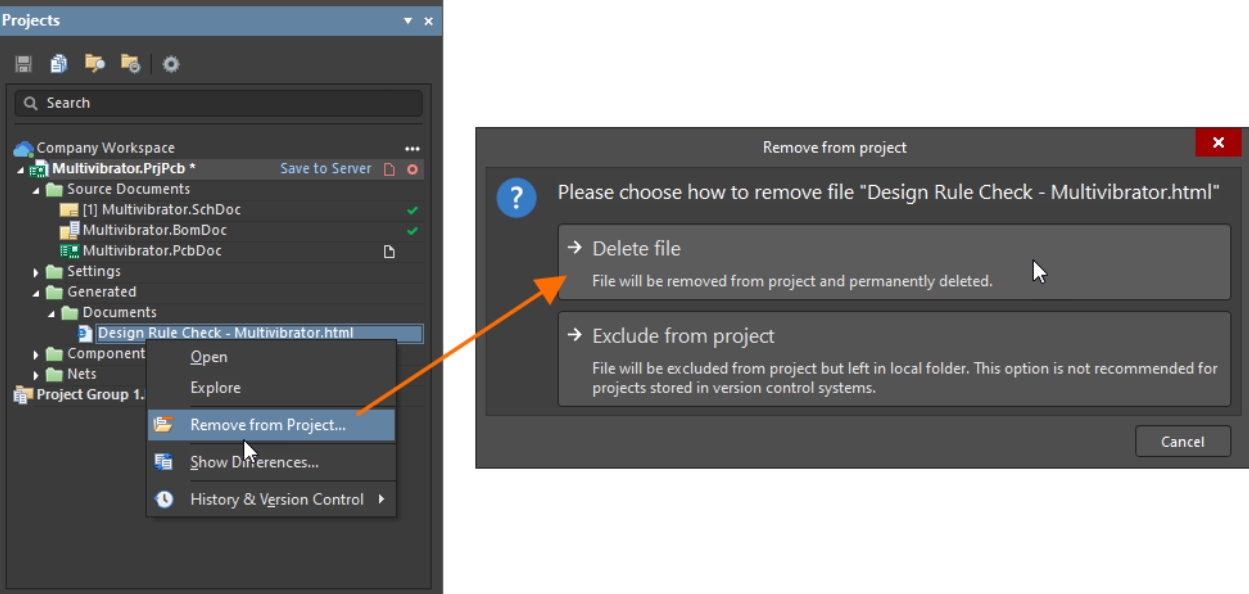

سپس فایل گزارش DRC تولیدشده را از پروژه حذف کنید. این فایل در فرآیند انتشار طراحی دوباره ایجاد خواهد شد. برای این کار، در پنل Projects به مسیر Generated\Documents بروید، روی فایل گزارش راستکلیک کرده و گزینهی Remove from Project را انتخاب کنید. در پنجرهی بازشده، Delete file را برگزینید.

تمام فایلهای باز را ببندید (با راستکلیک روی یکی از تبها و انتخاب Close All Documents).

در نهایت پروژه را در Workspace ذخیره کنید. برای این کار روی گزینهی Save to Server در کنار نام پروژه کلیک کرده، توضیحی مانند PCB design complete در فیلد Comment وارد کرده و روی OK بزنید.

قسمت بعدی: ایجاد نقشه فایل PCB (قسمت #9 آموزش آلتیوم دیزاینر)