Zynq چیست؟ آموزش کامل معماری Zynq

قبل از بررسی معماری Zynq باید بدانیم اصلا سیستم روی چیپ چیست و چطور اختراع شد. Zynq را میتوان یک سیستم روی چیپ (SoC) شامل معماری ARM و FPGA دانست. جهت درک بیشتر پیشنهاد میکنم مقاله FPGA چیست را بخوانید.

Zynq چیست؟

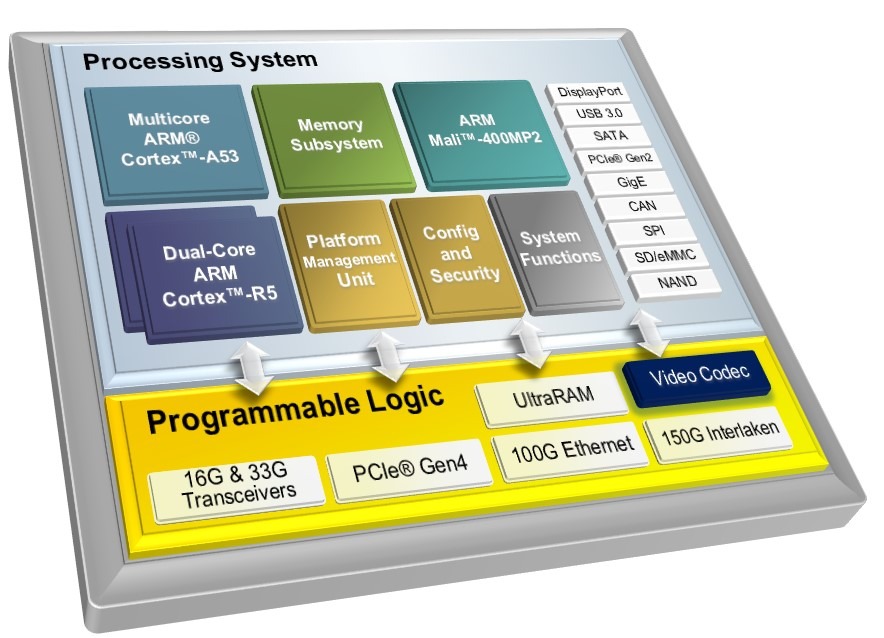

Zynq در حقیقت یک سیستم روی چیپ یا همان SoC است. در داخل ZYNQ یک میکروپروسسور سری ARM در کنار یک FPGA قرار دارد. هر جا که نیاز به پردازش موازی اطلاعات در کنار یک میکروکنترلر یا میکروپروسسور قدرتمند باشد، میتوانیم از چیپ ها با معماری Zynq استفاده کنیم. شما میتوانید با استفاده از زبان C و C++ به راحتی روی تراشه های Zynq برنامه نویسی کنید. تراشه ها با معماری Zynq انواع مختلفی دارند که هر کدام کاربرد های مخصوص خود را دارند. برخی از این تراشه ها در زیر لیست شده اند:

- Zynq-7000 SoC

- Zynq UltraScale+ MPSoC

- Zynq UltraScale+ RFSoC

- و …

معماری ZYNQ در حقیقت تلفیق دو هسته ARM Cortex-A9 با یک FPGA است. رابط (interface) مورد استفاده در این معماری AXI است که به علت پهنای باند بسیار زیاد و تاخیر بسیار کوتاه متداول شده و به عنوان رابط استاندارد در سیستم های جدید باعث کم شدن هزینه و اندازه فیزیکی سیستم می شود.

در داخل تراشه های Zynq انواع مختلفی از موارد پرکاربرد وجود دارد که در ادامه به آنها میپردازیم. از معماری Zynq در پردازش تصویر، یادگیری ماشین، دوربین های حرفه، CNC و … استفاده میشود.

تاریخچه سیستم روی چیپ (SoC)

اکثر افراد ترجیح می دهند قطعات الکترونیکی با اندازه های کوچک داشته باشند. با این حال، قبل از گسترش رادیوهای کوچک، رادیوهای بزرگ استفاده می شدند. در آغاز پیدایش رادیو های فشرده، کسانی که رادیو های بزرگ را ترجیح میدادند از رادیو های فشرده استفاده نمی کردند. اما، با مرور زمان مزایای داشتن یک رادیوی فشرده منجر به تولید قطعات کوچک تر شد. امروزه با پیشرفت تکنولوژی، شرکتهای سازنده توانایی اضافه کردن بخش های مختلف یک سیستم به قطعات کوچک تر را دارند که همگی به یک چیپ تبدیل میشوند، و به عنوان سیستم بر روی چیپ (SoC) در الکترونیک شناخته می شوند.

پیش از اختراع Zynq، پردازندهها با FPGA همراه بودند که ارتباط بین سیستم منطق (PL) و سیستم های پردازش (PS) را پیچیده میکرد. معماری Zynq، آخرین نسل از Xilix سیستم های قابل برنامه ریزی بر روی چیپ (soc)، ترکیب پردازنده های دو هسته ای ARM کورتکس A9 با پردازش (FPGA) است. رابط مورد استفاده در معماری Zynq بر پایه استاندارد AXI (Advanced eXtensible Interface) است که پهنای باند بالا و تاخیر کم را فراهم می کند.

قبل از قرار دادن پردازنده ARM داخل تراشه Zynq، کاربران از یک هسته نرم افزاری میکروپروسسور Xilix مثل Microblaze استفاده می کردند. مزیت اصلی استفاده از Microblaze، انعطاف پذیری نمونههای پردازنده در یک طراحی است. از سوی دیگر، حافظه سخت افزاری در Zynq باعث بهبود عملکرد قابل توجهی می شود. قرارگیری قطعات در یک چیپ، هزینه کلی و اندازه فیزیکی دستگاه را کاهش می دهد.

روند طراحی معماری Zynq

پروسه طراحی معماری Zynq دارای چند مرحله مشترک با یک FPGA معمولی است. مرحله اول تعریف ویژگی ها و الزامات سیستم است. در مرحله بعدی، در طول مرحله طراحی سیستم، وظایف مختلف (توابع) برای پیادهسازی در هر دو بخش PL یا PS اختصاص داده می شود که پارتیشن بندی وظیفه (task partitioning) نامیده می شود. این مرحله مهم است زیرا عملکرد کلی سیستم نیاز به اجرای توابع و وظایف آن در تکنولوژی مناسبی دارد: سختافزار یا نرمافزار !

سپس، سخت افزار و توسعه نرم افزار و آزمایش باید انجام شود. با توجه به PL، وظیفه شناسایی بلوک های عملکردی مورد نیاز برای رسیدن به مشخصه های طراحی و همچنین مونتاژ آن ها به عنوان IP و ایجاد ارتباط مناسب بین آن ها است.

به همین ترتیب، تغییرات نرمافزار برای توسعه کد باید روی PS اجرا شود. در نتیجه، یکپارچه سازی سیستم و آزمایش لازم است تا طراحی کامل شود. شکل 2 نمودار طراحی Zynq SoC را نشان میدهد.

درون zynq چه میگذرد؟

بخش های PS و PL قسمتی از ZYNQ هستند که توضیح داده میشوند.

واحد پردازش برنامه (APU)

هر APU از دو پردازنده ARM کورتکس A9 که هر کدام از آن ها به طور کلی شامل واحد neon، واحد ممیز شناور (FPU)، واحد مدیریت حافظه (MMU) و حافظه پنهان L1 است تشکیل می شود. علاوه بر این، APU شامل کنترل snoop و حافظه پنهان L2 است. شکل 3 ساختار APU را نشان میدهد.

- NEON: یک دستور چند داده (SIMD)، توسط این واحد ارائه می شود که شتاب عمده الگوریتمهای DSP و رسانه را به پردازشگر اصلی ARM میآورد.

- FPU: این واحد شتاب عملیات نقطه شناور را فراهم میکند.

- حافظه پنهان L1: هر پردازنده دستورالعمل های خاص و داده های پنهان، برای ذخیرهسازی دستورالعمل ها و داده ها را دارد.

- MMU: وظیفه تبدیل حافظه مجازی به آدرس های حافظه فیزیکی دارد.

- واحد کنترل Snoop (SCU): ارتباط بین پردازنده های L2 و L3 یکی از وظایف اصلی SCU است.

- حافظه پنهان L2: بین دو پردازنده تقسیم می شود که آنها را قادر می سازد تا به جدیدترین آپدیت یک متغیر دسترسی داشته باشند.

ساختار منطق قابل برنامه ریزی (PLS)

مانند سایر FPGA، بخش منطقی قابلبرنامهریزی Zynq متشکل از بلوکهای منطقی قابل تنظیم (CLBs) است و دو برش دارد. هر برش شامل چهار جدول مراجعه ای (LUTs)، هشت فلیپ فلاپ (FFs)، و یک سوئیچ ماتریسی همراه(ضمیمه) است. علاوه بر این، بلوک های RAM و DSP نیز وجود دارند. شکل4، ساختار PL را نشان می دهد.

- Slice: هر برش قادر به اجرای مدار های ترکیبی و ترتیبی است.

- جدول مرجعه ای (LUT): برای اجرای یک تابع منطقی از شش ورودی، RAM، ROM یا شیفت رجیستر (ثبات انتقال دهنده) استفاده می شود.

- فلیپ فلاپ (FF): به عنوان یک بیت حافظه با قابلیت راه اندازی مجدد (reset) متوالی مورد استفاده قرار می گیرد.

- سوئیچ ماتریسی: رابط بین بخش های مختلف داخل، و بین CLB و دیگر بخش های PL است.

با سلام و عرض ادب خدمت شما. بنده دانشجو هستم و میخواستم در زمینه سیستمهای ناهمگن یا heterogeneous systems کار کنم این سیستم از FPGA و CPU استفاده میکنه اما من نمیدونم این کار در ایران شدنی هست یا خیر چون بردهایی که OpenCL رو ساپورت میکنن وحشتناک گرون هستن سوال من اینه که میشه این کار رو انجام داد بدون این که بردهای گرون رو تهیه کرد؟

سلام جناب مهندس رحیمی

شما امکان تدریس خصوصی دارید ؟

سلام عزیز

در حالت کلی خیر، اما با تلگرام پشتیبانی @irenxdotir در ارتباط باشید ممکن هست در مورد درخواست شما انجام بشه

آقای محمد رحیمی لطفا در اسرع وقت به نظر من پاسخ بده

سلام عزیز

کجا نظر گذاشتید؟